# A 24mW 2.5Gb/s VCSEL Driver in 0.18um CMOS

Jean-Philippe Thibodeau<sup>1</sup>, Chris Murray<sup>2</sup> and David V. Plant<sup>1</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, McGill University, Montreal, Canada

<sup>2</sup>Emcore Corporation, Albuquerque, New Mexico, USA

#### 1 INTRODUCTION

With the ever increasing processing capacity of digital systems, electrical interconnects linking CMOS chips have become the limiting performance factor. Optical interconnects have been proposed as a promising alternative to increase interconnect capacity [1]. Although vertical-cavity surface-emitting lasers (VCSEL) are well suited for such an application [1], high-speed VCSEL drivers reported in the literature generally consume a significant amount of power [2,3]. In this paper, the design and testing of a 2.5 Gb/s VCSEL driver for short-to-medium reach optical interconnects is outlined.

#### 2 CIRCUIT DESIGN

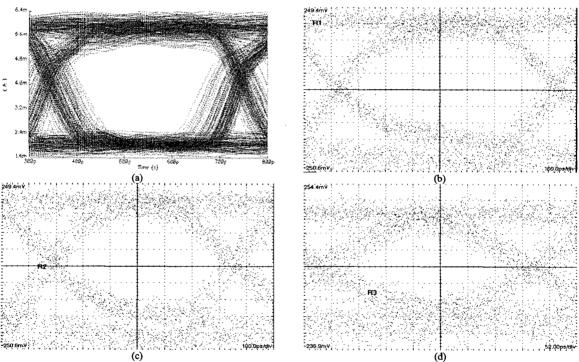

The driver is designed in a TSMC CMOS 0.18um process made available through the Canadian Microelectronics Corporation (CMC). The system-level topology of the driver is illustrated in figure 1 [4]. A low-voltage-differential-signal (LVDS) is applied to the inputs of the pre-amplifier stage, implemented as a common-gate amplifier. The pre-amplifier has a gain of 11dB and a 3dB bandwidth exceeding 2GHz. The pulse-shaping stage further amplifies the signal and distorts it to prevent the current steering transistors of the laser driver stage from entering into full cut-off. This leads to better symmetry in the rise and fall times of the generated optical signal. The laser driver consists of a conventional current-steering differential pair with a dummy PMOS load in one of the branches. The resulting modulated current is combined with a bias current generated on-chip and pulled directly from the VCSEL. All stages are designed in NMOS with PMOS loads and biased at maximum f<sub>T</sub> for optimum performance. A system simulation model, including models for the printed-circuit board (PCB) leads, ceramic quad-flat package (CFP) leads, VCSEL die, bond wire and extracted chip parasitics, was developed in Cadence and simulated using Spectres. The simulated eye diagram of the current through the VCSEL is shown in figure 2(a) at 2.5 Gb/s. Although the driver can perform in excess of 5 Gb/s, laboratory experiments on the test fixture show eye closure and significant jitter around 3 Gb/s, which limit the performance of the system.

## 3 EXPERIMENTAL SETUP AND MEASUREMENT RESULTS

The fabricated driver chip was packaged in a CFP 80-pin package, along with a 10Gb/s VCSEL die provided by Emcore Corporation, and mounted on an RF test PCB. The VCSEL has a threshold current of 1mA and a slope efficiency of 0.5W/A. The LVDS input is applied with an Anritsu MP1763B pulse pattern generator through RF cables. The modulated optical signal is relayed to a New Focus 12GHz photoreceiver through a free-space two lens telecentric system with focal lengths of 15mm. In order to perform bit-error rate (BER) measurements, the photoreceiver output signal was further amplified with an RF amplifier. Eye diagram measurements were taken using a Tektronix 8000 communications signal analyzer. Measured eyes diagrams at 1.25Gb/s, 1.5Gb/s and 2.5Gb/s are provided in figures 2(b), 2(c) and 2(d) respectively. BER measurements at various pseudo-random bit sequence lengths for the three bit rates mentioned above along with power consumption measurements are included in table 1. BER measurements at 2.5Gb/s were unavailable at the time of submission due to measurement issues. Power consumption measurements include the VCSEL modulation and bias currents, which represent 75% of the total power consumption. The average optical power emitted by the VCSEL is 2mW at 2.5Gb/s. We expect to achieve better data rates and BER in the future by probing the inputs of the driver or using a higher bandwidth test fixture.

## 4 CONCLUSIONS

We have outlined the design and test of a 2.5Gb/s VCSEL driver in 0.18um CMOS. It consumes an average of 24.2mW at 2.5Gb/s for an average emitted optical power of 2mW, which compares advantageously with other published designs [2,3].

### 5 REFERENCES

- [1] D.A.B. Miller, "Rationale and challenges for optical interconnects to electronic chips," Proc. IEEE, vol. 88, no. 6, pp.728-749, June 2000.

- [2] F. Delpiano, B. Bostica, M. Burzio, P. Pellegrino, and L. Pesando, "10-Channel optical transmitter module operating over 10Gb/s based on VCSEL and hybrid integrated silicon optical bench," Proc. Electronic Components and Technology Conference, 1999, pp.759-762.

- [3] D.V. Plant, A.E.L. Chuah, M.B. Venditti, and A.D. Isac, "2.5 Gb/s CMOS push-pull VCSEL driver with symmetric rising and falling edges," Applied Optics, in press.

- [4] K.R. Shastri, K.A. Yanushefski, J.L. Hokanson, and M.J. Yanushefski, "4.0Gb/s NMOS laser driver," Proc. IEEE Custom IC Conference, 1989, pp. 14.7.1-3.

Acknowledgments: This work was partially supported by the National Sciences and Engineering Research Council (NSERC) and industrial partners, through the Agile All-Photonic Networks (AAPN) Research Network, the Canadian Microelectronics Corporation (CMC), and a NSERC graduate scholarship. We also thank Julien Faucher and Eric Bisaillon for their help in setting up the experiments.

Figure 1: System-level topology of the VCSEL driver

Figure 2: Eye diagrams at various data rates (a) Simulated at 2.5Gb/s (b) Measured at 1.25Gb/s (c) Measured at 1.5Gb/s (d) Measured at 2.5 Gb/s

| Data Rate | PRBS Length        | BER                 | Total Power<br>Consumption |

|-----------|--------------------|---------------------|----------------------------|

| 1.2 Gb/s  | 2 <sup>31</sup> -1 | < 10 <sup>-10</sup> | 19.8mW                     |

| 1.5 Gb/s  | 2 <sup>15</sup> -1 | < 10 <sup>-9</sup>  | 22.9mW                     |

| 1.5 Gb/s  | 29-1               | < 10 <sup>-12</sup> | 22.9mW                     |

| 2.5 Gb/s  | TBD                | TBD                 | 24.2mW                     |

Table 1: Bit-error rate and power consumption measurements for three data rates